OrCAD Pspice-Capacitors

capacitor의 특성을 알아보고 pspice에 적용하여 특성을 증명하고 계산값과 비교한다.

Capacitor RC 직렬회로

pspice를 이용하여 pulse 전압원 1개, 저항 1개, capacitor 1개, 0V Ground 1개로 RC 직렬회로를 아래와 같이 구성한다.

Pulse 전압원을 사용할 때 place-> pspice component-> modeling application->source ->independent source를 이용하여 값을 설정한다. Pulse를 클릭하여 step 함수를 설정할 수 있는데 V1=0, V2=10V 이외의 나머지 Delay, Rise Time, AC,DC 값들은 디폴트 값으로 설정해준다. Place 버튼을 클릭하면 pspcie 회로에 설치가 가능하다. 이렇게 pulse 전압원을 그림2와 같이 위치하도록 한다.

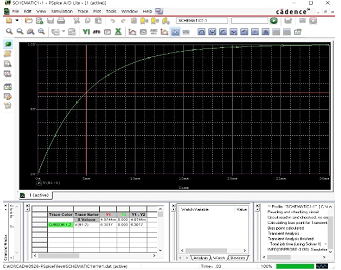

회로를 구성했다면 Simulation setting을 analysis Time Domain으로 하여 Run to Time을 30ms로 설정하고 나머지 값들은 디폴트값으로 시뮬레이션을 진행한다. New simulation을 만들고 나서 전압, 전류 핀을 고정시켜주고 디버깅을 시작한다. 전류핀을 꽂을 때는 와이어에 위치시키는 것이 아니라 저항 부품 끝에 위치하도록 하는 것에 유의하도록 한다. 결과는 대략적으로 예측하여 그려본 다음처럼 나올 것이다.

simulation 결과 같은 파형 모양을 볼 수 있다. 여기서 Trace-> cursor-> display로 커서를 활성화 시켜주고 위에 보이듯이 초록커서는 x=0 y=0에 위치시키고 빨간커서는 6.3V에 최대한 가깝게 위치시켜준다. 그럼 보이는 값들이 출현한다. 6.3017에 위치 시키면 시정수의 값이 4.9745ms가 됨을 볼 수 있다. 또한 Ic(t)곡선으로도 시정수의 값을 구할 수 있다.

Vc(t) 곡선에서 6.3V가 되는 시간(63% of 10[V])과 Ic(t) 곡선에서 7.3mA가 되는 시간(73% of 10[mA])은 모두 시정수(τ=RC)와 동일하다. 이들을 증명하기 위해 직접 계산해보면 다음과 같이 나타난다. (1)Vsmax=10V (2)시정수=RC=500*10*10^-6=5*10^-3=5ms 를 가진다. 측정값과는 미세한 차이가 있는데 이는 오차가 발생하였기 때문이다 오차발생이유는 고찰에서 언급하도록 하겠다. 계산한 시정수값에 대하여 직접 그래프를 그려보면 모양의 그래프가 그려진다.

다른 실험으로 C1 = 10uF에서 R1 = 500, 1k, 2k으로 조건을 바꾸어 시정수(τ)를 측정하고 R1 = 500에서 C1 = 10uF, 20uF, 30uF으로 조건을 바꾸어 시정수(τ)를 측정을 해본 결과 아래의 그림들과 같은 결과를 보았다.

각 그래프에서 커서를 활성화 시켜 시정수를 측정한 결과 위 표와 같이 나타나게 되었다. 500옴 10uF일 때는 시정수 4.9745ms, 500옴 20uF일 때는 시정수 9.962ms, 500옴 30uF일 때는 시정수 14.927ms, 1k옴 10uF일 때는 시정수 9.951ms, 2k옴 10uF일 때는 시정수 19.902ms의 값이 측정되었다. 직접 계산한 값들과 비교한 결과 근사치에 도달했다는 것을 볼 수 있다. 여기서 완변히 계산값과 일치하지 않는 오차이유에 대해서는 고찰에서 서술하겠다. 또한 이 부분에서도 Vc(t) 곡선에서 6.3V가 되는 시간(63% of 10[V])과 Ic(t) 곡선에서 7.3mA가 되는 시간(73% of 10[mA])은 모두 시정수(τ=RC)와 동일함을 볼 수 있었다. 그리고 분석을 해보면 저항이 500옴으로 고정에서 C값이 커지면 시정수가 커졌고 C값 고정에서 저항의 값을 올린 결과도 시정수가 커졌다. 이를 통해 식 τ = RC ( 시정수 )을 증명할 수 있었고 그래프의 모양도 다음 식(1),(2)에 만족하며 변하는 것을 확인할 수 있었다. Vc와 Ic의 관계를 설명해보면 전류가 유입되더라도 전압은 전류 축적이 있어야 서서히 증가한다. 전압이 변하지 않으면 전류는 흐르지 않는다.

결론 및 고찰

위 실험은 펄스 전압원을 통해서 캐패시터의 변화를 보는 실험이였다. 실험결과 첫번째 실험은 시간이 지날수록 전압이 증가하였고 두번째 실험은 전압이 감소하였다. 이 실험은 펄스회로의 미분회로와 적분회로를 알아보는 실험이였다. 그 결과 알게 된 점은 적분회로는 R이 앞에 있고 C가 뒤에 연결되어 있다. 이는 적분 파형 또한 적분의 특성을 가졌다. 미분회로와는 반대로 파형을 보여준다. 그리고 위 실험에서 오차가 발생함을 발견할 수 있는데 이는 커서의 표현할 수 있는 값이 미세하게 측정이 불가능하기 때문에 오차가 발생하였다. 이는 V값과 t값을 미세하게 측정할 수 있도록 설정한다면 오차가 줄어들 것이다.

※무단 복제 및 공유를 불허합니다.

'Information Communication Technology > Orcad' 카테고리의 다른 글

| OrCAD Pspice-Capacitor와 Inductor를 이용한 회로 구현 (0) | 2022.09.29 |

|---|---|

| OrCAD Pspice-Inductors (0) | 2022.09.29 |

| OrCAD Pspice-Series_RC_Circuits (0) | 2022.09.28 |

| OrCAD Pspice 옴의 법칙과 키르히호프의 법칙 회로 설계 (0) | 2022.09.28 |

| OrCAD Pspice 설계 연습 (0) | 2022.09.28 |